El acceso

directo a memoria (DMA, del inglés direct memory access) permite a cierto tipo

de componentes de una computadora acceder a la memoria del sistema para leer o

escribir independientemente de la unidad central de procesamiento (CPU). Muchos

sistemas hardware utilizan DMA, incluyendo controladores de unidades de disco,

tarjetas gráficas y tarjetas de sonido. DMA es una característica esencial en

todos los ordenadores modernos, ya que permite a dispositivos de diferentes

velocidades comunicarse sin someter a la CPU a una carga masiva de

interrupciones.

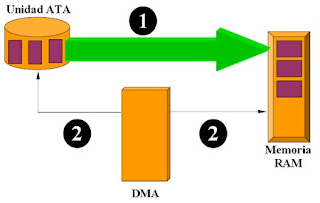

Una

transferencia DMA consiste principalmente en copiar un bloque de memoria de un

dispositivo a otro. En lugar de que la CPU inicie la transferencia, la

transferencia se lleva a cabo por el controlador DMA. Un ejemplo típico es

mover un bloque de memoria desde una memoria externa a una interna más rápida.

Tal operación no ocupa al procesador y, por ende, éste puede efectuar otras

tareas. Las transferencias DMA son esenciales para aumentar el rendimiento de

aplicaciones que requieran muchos recursos.

- PROBLEMAS DE COHERENCIA EN LA MEMORIA CACHE

La DMA

puede llevar a problemas de coherencia de caché. Imagine una CPU equipada con

una memoria caché y una memoria externa que se pueda acceder directamente por

los dispositivos que utilizan DMA. Cuando la CPU accede a X lugar en la

memoria, el valor actual se almacena en la caché. Si se realizan operaciones

posteriores en X, se actualizará la copia en caché de X, pero no la versión de

memoria externa de X. Si la caché no se vacía en la memoria antes de que otro

dispositivo intente acceder a X, el dispositivo recibirá un valor caducado de

X.

Del mismo

modo, si la copia en caché de X no es invalidada cuando un dispositivo escribe

un nuevo valor en la memoria, entonces la CPU funcionará con un valor caducado

de X.

Este

problema puede ser abordado en el diseño del sistema de las siguientes dos

formas:

Los

sistemas de caché coherente implementan un método en el hardware externo

mediante el cual se escribe una señal en el controlador de caché, la cual

realiza una invalidación de la caché para escritura de DMA o caché de descarga

para lectura de DMA.

Los

sistemas no-coherente dejan este software, donde el sistema operativo debe

asegurarse de que las líneas de caché se vacían antes de que una transferencia

de salida de DMA sea iniciada y anulada antes de que una parte de la memoria

sea afectada por una transferencia entrante de DMA que se haya requerido. El

sistema operativo debe asegurarse de que esa parte de memoria no es accedida

por cualquier subproceso que se ejecute en ese instante. Este último enfoque

introduce cierta sobrecarga a la operación de DMA, ya que la mayoría de

hardware requiere un bucle para invalidar cada línea de caché de forma

individual.

Los

híbridos también existen, donde en la caché secundaria L2 es coherente,

mientras que en la caché L1 (generalmente la CPU) es gestionado por el

software.

- SECUENCIA DE EVENTOS

Una

operación de E/S por DMA se establece ejecutando una corta rutina de

inicialización. Consiste en varias instrucciones de salida para asignar valores

iniciales a:

AR:

Dirección de memoria de la región de datos de E/S IOBUF (buffer de

entrada/salida).

WC: Número

N de palabras de datos a transferir.

Una vez

inicializado, el DMA procede a transferir datos entre IOBUF y el dispositivo de

E/S. Se realiza una transferencia cuando el dispositivo de E/S solicite una

operación de DMA a través de la línea de petición del DMAC.}

Después de

cada transferencia, se decrementa el valor de WC y se incrementa el de AR.

La

operación termina cuando WC=0, entonces el DMAC (o el periférico) indica la

conclusión de la operación enviando al procesador una petición de interrupción.

- SECUENCIA DE EVENTOS DETALLADA

El procesador

inicializa el DMAC programando AR y WC.

El

dispositivo de E/S realiza una petición de DMA al DMAC.

El DMAC le

responde con una señal de aceptación.

El DMAC

activa la línea de petición de DMA al procesador.

Al final

del ciclo del bus en curso, el procesador pone las líneas del bus del sistema

en alta impedancia y activa la cesión de DMA.

El DMAC

asume el control del bus.

El

dispositivo de E/S transmite una nueva palabra de datos al registro intermedio

de datos del DMAC.

El DMAC

ejecuta un ciclo de escritura en memoria para transferir el contenido del

registro intermedio a la posición M[AR].

El DMAC

decrementa WC e incrementa AR.

El DMAC

libera el bus y desactiva la línea de petición de DMA.

El DMAC

compara WC con 0:

Si WC >

0, se repite desde el paso 2.

Si WC = 0,

el DMAC se detiene y envía una petición de interrupción al procesador.

MOTOR DE

ACCESO DIRECTO A MEMORIA:

Además de

la interacción de hardware, el acceso directo a memoria puede ser utilizado

para descargar costosas operaciones de memoria, tales como copias de gran

tamaño u operaciones de dispersión-reunión, desde la CPU a un motor de acceso

directo a memoria dedicada. Intel incluye estos motores en los servidores de

gama alta, llamado I/O Acceleration Technology (IOAT).

- TRANSFERENCIAS:

Durante las

operaciones del DMA, el rendimiento del sistema puede verse afectado debido a

que este dispositivo hace un uso intensivo del bus y por lo tanto la cpu no

puede leer datos de memoria, por ejemplo para leer la siguiente instrucción a

ejecutar. Esto provoca que mientras el DMA está operando, la cpu deba esperar a

que finalice dicha tarea sin ejecutar ninguna instrucción. Para solventar esto,

existe una memoria cache dentro de la CPU que permite a ésta seguir trabajando

mientras el DMA mantiene ocupado el bus.

En

computadores que no disponen de memoria cache,el DMA debe realizar su tarea

evitando ocupar el bus de datos mientras la CPU realiza la fase de captación de

la instrucción. A partir de estas dos posibilidades, existen dos tipos de

transferencias de datos del DMA:

TRANSFERENCIAS

MODO RÁFAGA: una vez que la CPU concede el bus al DMA, este no lo libera hasta

que finaliza su tarea completamente. Este tipo de transferencia se usa en

sistemas que disponen de una memoria cache en la unidad de procesamiento, ya

que mientras la CPU puede seguir trabajando utilizando la cache.

TRANSFERENCIAS

MODO ROBO DE CICLO: una vez que la CPU concede el bus al DMA, este lo vuelve a

liberar al finalizar de transferir cada palabra. Teniendo que solicitar de

nuevo el permiso de uso del bus a la CPU. Esta operación se repite hasta que el

DMA finaliza la tarea. Este tipo de transferencia se suele usar en sistema que

no disponen de memoria cache en la unidad de procesamiento, ya que de este

modo, aunque la transferencia de datos tarda más en realizarse, la CPU puede

seguir ejecutando instrucciones.

No hay comentarios:

Publicar un comentario